# Low Power Control IC for Efficient High-Voltage Piezoelectric Driving in a Flying Robotic Insect

Michael Karpelson, Robert J. Wood, Gu-Yeon Wei

School of Engineering and Applied Sciences, Harvard University, Cambridge, MA, USA E-mail: michaelk@seas.harvard.edu

# Abstract

A dual-channel, low power control IC for driving high voltage piezoelectric actuators in a flapping-wing robotic insect is presented. The IC controls milligram-scale power electronics that meet the stringent weight and power requirements of aerial microrobots. Designed in a 0.13 $\mu$ m CMOS process, the IC implements an efficient control algorithm to drive piezoelectric actuators with high temporal resolution while consuming <100 $\mu$ W during normal operation at 1.0V.

*Keywords:* low power, SOC, high voltage, piezoelectric actuator, and microrobotics.

## Introduction

Flapping-wing robotic insects are micro air vehicles inspired by biological insects and useful for exploration, environmental monitoring, search and rescue, and surveillance. The Harvard Microrobotic Fly (HMF) is the first robotic insect capable of lift-off with external power [1]. The wing flapping motion in the HMF is powered by piezoelectric actuators, which offer good mechanical performance but present a number of challenges from a power electronics perspective, including the need for high voltage drive signals (200-300V) and recovery of unused energy from the actuator [2].

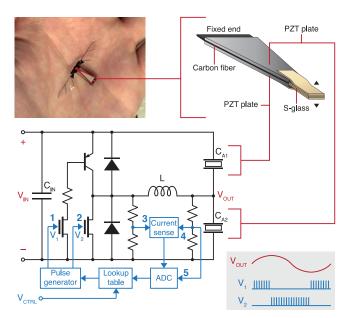

Fig. 1 shows the HMF and the structure of the actuator used in the robot. A voltage applied across one of the PZT layers causes the tip of the actuator to deflect (details in [3]). Also shown is a half-bridge switching drive circuit that can be used to drive the actuator from high voltage supply V<sub>IN</sub>. The circuit, described fully in [2], is one of several previously developed power circuits that, when combined, are capable of stepping up a 3.7V Li-poly battery output to 200V and generating an arbitrary drive signal for the actuator. Careful selection of switching topologies, fabrication of custom magnetic components, and lightweight circuit integration techniques allow the power circuits to meet the stringent weight and power demands of hovering flight [4]. In previous work, the control functionality for the power circuits was implemented using an external high-performance, high power microcontroller.

This paper presents a custom low power control IC for onboard integration with the HMF. To efficiently generate arbitrary drive signal waveforms that power the wing flapping motion, the power circuits require high timing resolution and precision; at the same time, the control IC is subject to strict weight and area constraints and must consume a negligible amount of power compared to the actuator itself.

# System Architecture and Circuit Design

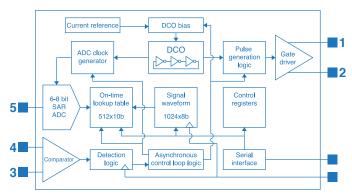

The IC contains two drive channels that share a current reference, a control register bank, and a serial programming interface. Fig. 2 shows a block diagram of a single drive channel. The controller modulates the power switches in Fig. 1 in such a way as to drive  $V_{\rm OUT}$  (the voltage at the central terminal of the actuator) towards its desired value, represented by the digital signal  $V_{\rm CTRL}$ . This is accomplished via successive iterations of a four-phase control algorithm—*Acquisition*,

Fig. 1. Robotic insect, piezoelectric actuator, drive circuit, and control architecture (numbers correspond to chip I/O in Fig. 2).

Fig. 2. Block diagram of single channel (I/O numbered as in Fig. 1).

Lookup, Charge, and Discharge [2]—to drive the actuator with low-frequency periodic signals (e.g., 50-200Hz).

During the Acquisition phase, a SAR ADC with a speed of up to 200kSps and a selectable resolution of 6-8 bits, samples V<sub>OUT</sub> via a resistive divider. Since V<sub>OUT</sub> changes by less than 2 ADC LSBs between successive Acquisition cycles, built-in ADC logic records the previous conversion value and operates as a delta-encoded ADC at the beginning of each new Acquisition phase. This reduces ADC conversion time to 2-4 ADC clock cycles in most cases. If the delta-encoded search fails due to an abnormal event (e.g., external stimulation of the actuator) the ADC reverts to a binary search algorithm, more typical of SAR ADCs, after a selectable number of cycles (up to 8).

During the Lookup phase, the ADC result, along with the digital signal  $V_{CTRL}$ , is used to address a lookup table (LUT) that stores pre-computed on-times for the switches. The on-

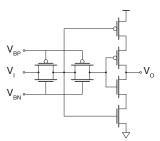

Fig. 3. DCO delay element with reduced short-circuit current.

times depend on inductance L and actuator capacitances  $C_{A1}$  and  $C_{A2}$ . The IC can control various actuator drive circuit topologies by appropriately programming on-times into the LUT (details in [2]). The LUT is implemented using a 512x10bit SRAM. A second 1024x8bit SRAM stores (optionally) drive signal waveforms (i.e., sequences of  $V_{CTRL}$ ).

During the Charge phase, turning on the appropriate switch for the time obtained from the LUT stores energy in the inductor. Then, the Discharge phase transfers energy stored in the inductor to the output or returns it to the supply, driving  $V_{OUT}$  towards  $V_{CTRL}$ . A current sense circuit detects when inductor current has reached zero by using a rail-to-rail comparator that monitors the voltages at the inductor terminals; this initiates a new control cycle. If the comparator fails to trigger, a fail-safe timer kicks the controller into the Acquisition phase after a safe amount of time.

The control algorithm imposes many timing requirements, including generating the pulses in the Charge phase and providing a clock for the ADC. To allow inductor current *i* to reach the correct level in conditions of high *di/dt* (short pulses), 10ns resolution is required. Lower resolution is acceptable at lower *di/dt* (longer pulses). During Charge, a wide tuning range digitally-controlled oscillator (DCO) operates at 50MHz with 50% duty cycle, allowing for 10ns resolution, and at 25MHz at low *di/dt* conditions to reduce power consumption. During Acquisition, the DCO operates at 5MHz and is further divided down to generate the ADC clock. The DCO comprises single-ended variable resistance delay elements [5] to reduce short-circuit current (Fig. 3), resulting in a power savings of over 35% compared to inverter-based delay stages. The DCO is disabled during Discharge.

The control loop logic relies on S-R latches to enable a semi-asynchronous architecture that, along with the variable-speed DCO, provides high temporal resolution without the need for a global high-speed clock. When the optional signal waveform SRAM is used, a sub-100kHz external clock is required for accurate timing of the stored  $V_{\text{CTRL}}$  sequence.

To reduce switching losses (e.g., due to ADC error), an optional mode keeps track of previous  $V_{CTRL}$  samples and suppresses pulses that lower  $V_{OUT}$  during periods when  $V_{CTRL}$  is monotonically increasing or, conversely, pulses that raise  $V_{OUT}$  when  $V_{CTRL}$  is monotonically decreasing. This reduces errant pulses, but also reduces the capability of the controller to compensate for unexpected changes in  $V_{OUT}$ .

## **Experimental Results**

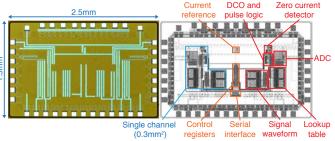

The dual-channel control IC is fabricated in  $0.13\mu m$  CMOS technology and occupies  $0.66mm^2$  ( $2.5\times1.5mm$  die). The die photograph and layout are shown in Fig. 4. When driving an actuator with a 100Hz sinusoidal signal, the IC consumes less than  $50\mu W/channel$  at 1.0V. Table I lists the power consumption of individual blocks and operating modes. Despite the high power draw of the DCO at 50MHz, incorporating lower-

| TADIET | DOMED  | DICCIDATION |

|--------|--------|-------------|

| LABLET | ·POWER | DISSIPATION |

| Current reference | 8.9µW | Zero current detector | 11µW        |

|-------------------|-------|-----------------------|-------------|

| DCO (5MHz)        | 79μW  | Leakage (2 channels)  | $21\mu W$   |

| DCO (50MHz)       | 732μW | ADC (8-bit mode)      | $3.2 \mu W$ |

| Aggregate         | 60µW  | Aggregate             | 98uW        |

| (single channel)  | ουμ w | (dual channel)        | 98µ W       |

Fig. 4. Die photograph (left) and diagram (right).

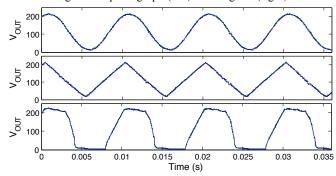

Fig. 5. Scope traces of three drive signal profiles on  $V_{OUT}$  (sinusoidal, triangular, and square wave).

Fig. 6. High-speed video frames of HMF wings flapping at 100Hz (asymmetry is due to manufacturing imperfections).

frequency operating modes and disabling the DCO during Discharge results in low aggregate power consumption.

Fig. 5 presents three different drive signal profiles measured from the circuit topology (control IC and switching converter) in Fig. 1 that drives capacitive loads representing a piezoelectric actuator. The third waveform (square wave) illustrates the finite slew rate of the overall drive circuitry. When attached to a real actuator, the control IC successfully flaps the HMF wings. High-speed video frames of wing motion from a sinusoidal  $V_{\rm CTRL}$  signal are shown in Fig. 6. Along with previous advances in lightweight high voltage drive circuits [4], the control IC enables a milligram-scale power electronics package suitable for flight testing in a flapping-wing robotic insect.

## References

- [1] R.J. Wood, "Liftoff of a 60mg flapping-wing MAV," IROS 2007.

- [2] M. Karpelson, et al., "Milligram-scale high-voltage power electronics for piezoelectric microrobots," ICRA 2009.

- [3] R.J. Wood, et al., "Optimal energy density piezoelectric bending actuators," Sensors & Actuators: A. Physical, Feb. 2005.

- [4] M. Karpelson, et al., "Design and fabrication of ultralight high-voltage power circuits for flapping-wing robotic insects," to appear APEC 2011.

- [5] M.-L. Sheu, *et al.*, "Wide frequency range voltage controlled ring oscillators based on transmission gates," *ISCAS* 2005.